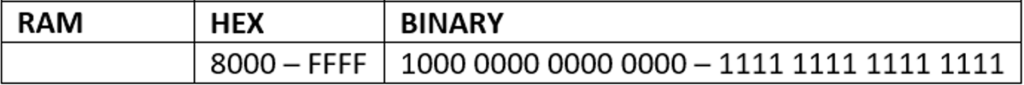

If we look at the figure to achieve the required address space, we can see that it is a 32K space characterized by a value 1 of the high order bit. Using linear addressing, we will invert the A15 bit of the address bus and connect it to the inverted CS pin to activate the chip. To ensure that the chip is enabled only in case of memory addressing, we will use the inverted MREQ signal and connect it to the inverted OE pin, using the same approach as with the ROM module. Since the RAM module can read and write, we will connect the inverted W pin to the inverted WR control signal of the control bus